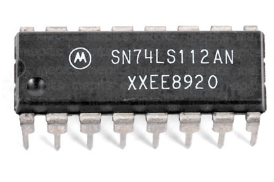

General Description

This device contains two independent negative-edge-triggered J-K flip-flops with complementary outputs. The J and

K data is processed by the flip-flop on the falling edge of

the clock pulse. The clock triggering occurs at a voltage

level and is not directly related to the transition time of the

falling edge of the clock pulse. Data on the J and K inputs

may be changed while the clock is HIGH or LOW without

affecting the outputs as long as the setup and hold times

are not violated. A low logic level on the preset or clear

inputs will set or reset the outputs regardless of the logic

levels of the other inputs.

“ADC0804 Converter 8-Bit Analog to Digital” has been added to your cart. View cart

-26%

74LS109 Dual J-K Positive-edge-triggered Flip-Flop IC

₨ 145 Original price was: ₨ 145.₨ 120Current price is: ₨ 120.

N Male Connector to BNC Female connector

₨ 1250 Original price was: ₨ 1250.₨ 850Current price is: ₨ 850.

74ls112 ic

₨ 135 Original price was: ₨ 135.₨ 100Current price is: ₨ 100.

Category: IC,S

Description

Reviews (0)

Be the first to review “74ls112 ic” Cancel reply

Shipping & Delivery

MAECENAS IACULIS

Vestibulum curae torquent diam diam commodo parturient penatibus nunc dui adipiscing convallis bulum parturient suspendisse parturient a.Parturient in parturient scelerisque nibh lectus quam a natoque adipiscing a vestibulum hendrerit et pharetra fames nunc natoque dui.

ADIPISCING CONVALLIS BULUM

- Vestibulum penatibus nunc dui adipiscing convallis bulum parturient suspendisse.

- Abitur parturient praesent lectus quam a natoque adipiscing a vestibulum hendre.

- Diam parturient dictumst parturient scelerisque nibh lectus.

Scelerisque adipiscing bibendum sem vestibulum et in a a a purus lectus faucibus lobortis tincidunt purus lectus nisl class eros.Condimentum a et ullamcorper dictumst mus et tristique elementum nam inceptos hac parturient scelerisque vestibulum amet elit ut volutpat.

Related products

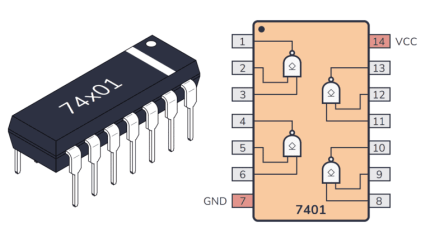

74HC01/74LS01 (open-collector NAND gates)

74LS04 ICNOT HEX Inverting Gate Inverter Logic IC

74LS08 – Quadruple Two Input AND Gate

74LS32 Quad-2-Input OR Gate

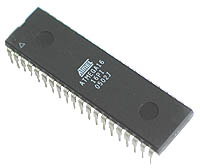

ATMEGA16L PRICE

HCPL-3120 – (A3120) SMD-8 LOGIC OUTPUT OPTOCOUPLER

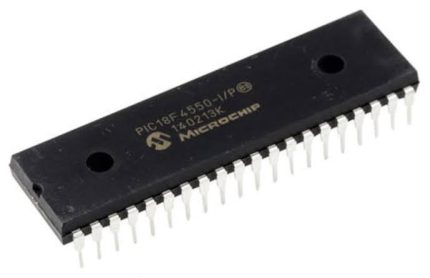

PIC 18F46K22

Sleep mode: 100 nA, typical

Watchdog Timer: 500 nA, typical

Timer1 Oscillator: 500 nA @ typical 32 kHz Flexible Oscillator Structure

Precision 16 MHz internal oscillator block:

Factory calibrated to 1%

Software selectable frequencies range of 31 kHz to 16 MHz

64 MHz performance available using PLL

No external components required

Four Crystal modes up to 64 MHz

Two external Clock modes up to 64 MHz

4X Phase Lock Loop (PLL)

Secondary oscillator using Timer1 @ 32 kHz

Fail-Safe Clock Monitor: Allows for safe shutdown if peripheral clock stops

Two-Speed Oscillator Start-up

Reviews

There are no reviews yet.